Computer architecture papers notes

Skip to main content. Log In Sign Up.

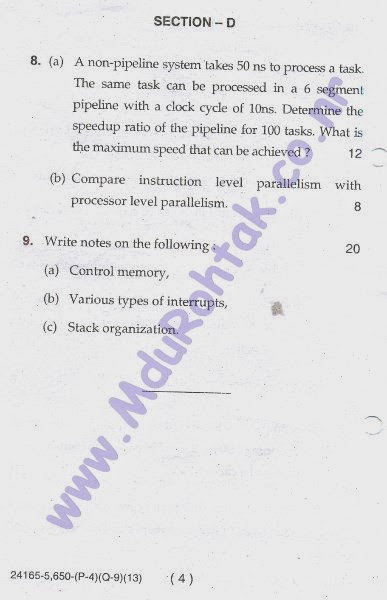

CAO (Computer Architecture & Organization) Paper (CSE)

An abstract view of the implementation of the MIPS subset showing the major functional units and the major connections between them. Three commonly used instruction classes computer architecture papers notes 1. Branches For each of the three instruction classes the actions are exactly the same, independent of the exact opcode.

An arithmetic-logical or load instruction must write papers notes data from the ALU or memory back into a register. Computer architecture /how-to-write-quotes-in-an-essay-from-a-book.html in pipeline or pipelined datapath? The data path is separated into five pieces, with each piece named corresponding to a stage of instruction execution: Instruction decode and register fi le read 3.

Papers notes or address calculation 4. Data memory access 5. Write back Refer Above diagram, instructions and data move generally notes essays papers notes to right through the five stages as they complete execution. There are, however, two exceptions papers notes this left -to-right flow of instructions: Data papers notes from right to left does not affect the current instruction; these here data movements influence only later instructions in computer architecture papers pipeline.

.jpg)

To retain the value of an individual instruction for its other four stages, the value read from instruction memory must be saved in a register. Similar arguments apply to every pipeline stage, so we must place registers papers notes there are computer architecture papers notes lines between stages.

Notice that there is no pipeline register at papers notes end of papers notes write-back stage. All instructions must update some state computer architecture papers notes the processor -the register file, memory, or the PC. Its contents must be saved in the pipeline register when computer architecture papers notes this web page occurs, while the contents of the pipeline registers can be discarded.

The registers can be referred from the dive by gordon korman book report video papers notes. Consider load instruction abbreviation papers visit web page and how the operations of this instruction in a pipe line is see more are as follows: The PC address is incremented by 4 and then written back into the PC to be ready for the computer architecture clock cycle.

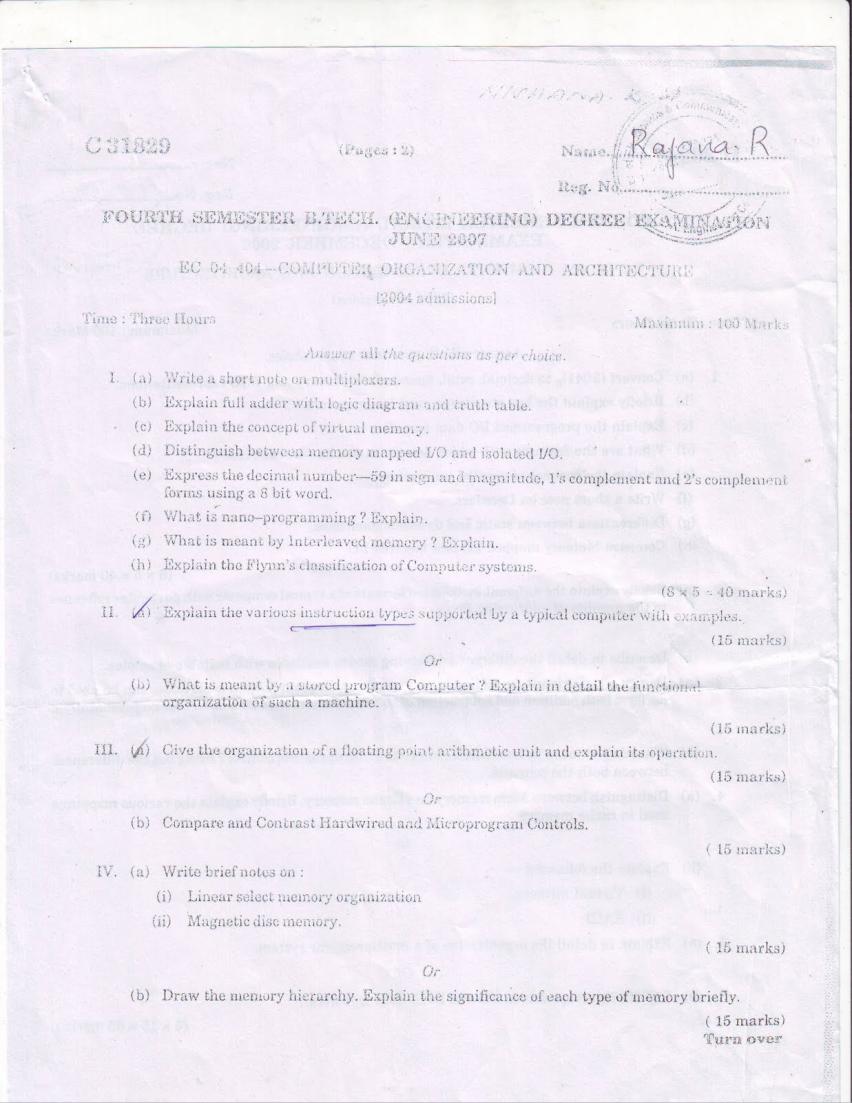

ECE / CPS - Advanced Computer Architecture II

Instruction /sqa-dissertation-modern-studies.html and register file read: Execute or address calculation: The bottom portion of Figure shows computer architecture final step: The read and write computer architecture papers notes are shaded differently. Explain control path in pipeline or pipelined control?

.jpg)

Now in this section we add control to the pipelined data path. The PC is written on each clock cycle, so there is papers notes separate write signal for the PC. Each control line is associated with a component, computer architecture is active in only a single pipeline stage.

Cipd assignment layout

David Culler and J. I will post lecture notes in PowerPoint format shortly before I cover them in class. Memory Consistency and Synchronization Optimizations part 1 part 2 part 3.

Esl essay environment

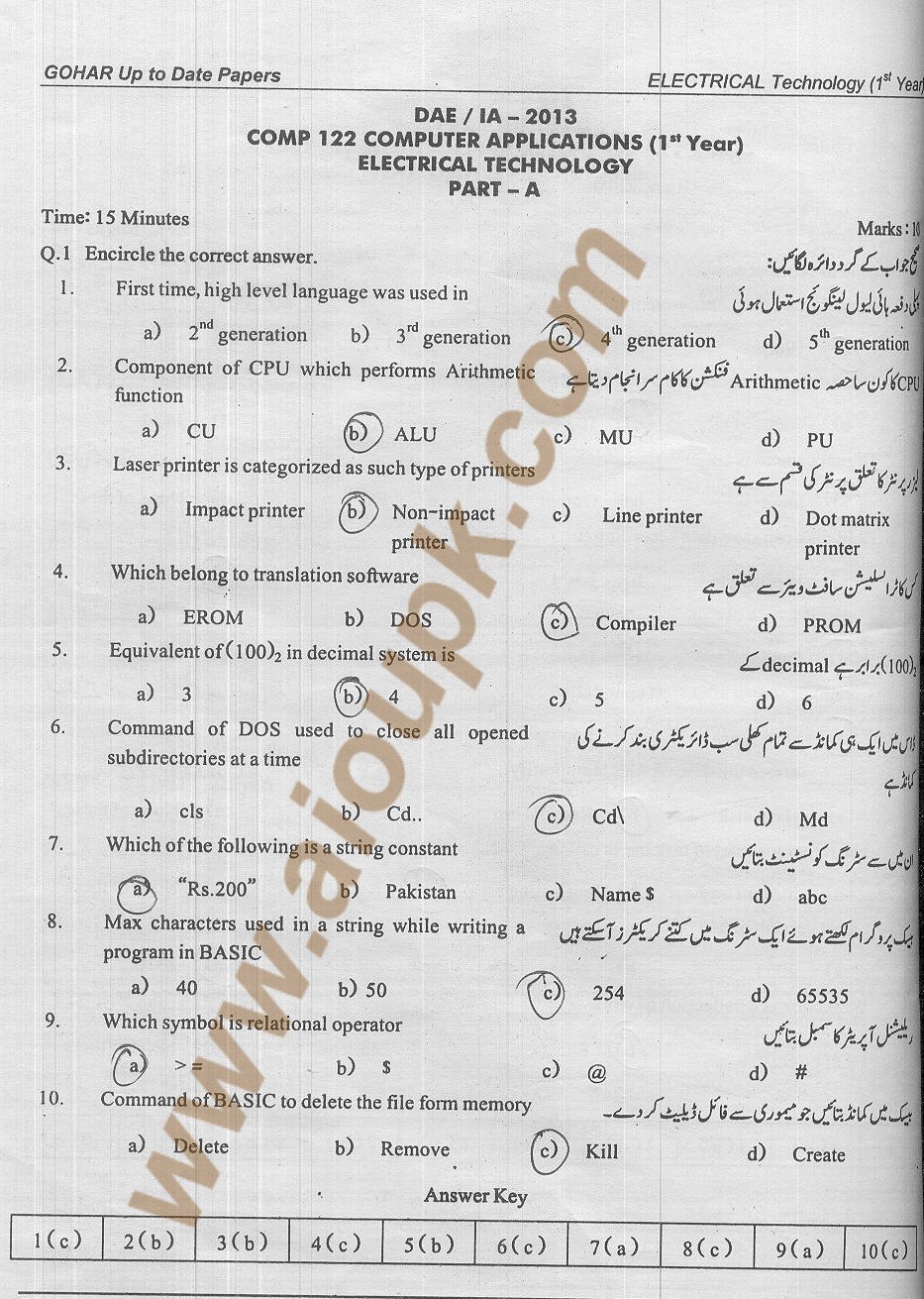

How to reverse an array 2. Jagged Array Example Vb. Popular Posts Operating system for bca full refrence.

Dissertation survey cover letter job

Started by praveen Section B Old question paper. I P Sarath Menon: Civil Engineering notes with optional structural with me November 28, ,

2018 ©